Libro de Arquitectura de Computadores

Fe de erratas de la edición 2017

Se incluyen sólo aquellas erratas que pueden inducir a error al alumno.

- Página 3. El tema aborda el problema ... a lo largo del

curso presente libro.

- Página 12. Comúnmente el rendimiento del computador ... el cociente entre la cantidad de trabajo

realizada realizado y el tiempo ...

- Página 13. La aceleración en el rendimiento es la razón ... Una

acelaración aceleración igual a 1 indica ....

- Página 16. Las mejoras expresadas en porcentaje a partir de la aceleración no son correctas (

15% y 25%). Para calcular la mejora en porcentaje habría que tomar (1 - 1/A). Los porcentajes deberían ser 13% y 20% respectivamente.

- Página 17. El tiempo de multitarea. Durante ... no

sólo solo la tarea que se utiliza para medir sobre la que se mide el tiempo de respuesta.

- Página 29. En este ejemplo, suponiendo que el registro PC vale 10000000

000000000h ... lo que resulta en un valor final para el PC de 10000000 000004000h 10000000 00000FA0h (que será múltiplo de 4).

- Página 36. La lógica para ejecutar ... en las líneas

las líneas Write.

- Página 36. El multiplexor sobre las líneas ... (bits 20 a 16 en

los accesos a las lecturas de memoria...

- Página 60. Resulta conveniente ...

del ciclo 5 al ciclo 4 del ciclo 6 al ciclo 5.

- Página 65. Las CPU actuales ... determinados tipos de excepciones.

- Página 68. En la figura 2.38 aparece el ciclo 9 cuando debería ser el 8.

- Página 78. A continuación, se estudian algunas técnicas para la reducción...

- Página 81. La ruta de reenvío MEM->ID no existe, pues no es necesaria.

- Página 83. Figura 2.54. ...

Se asume que el salto no se toma El salto no se toma.

- Página 83. La predicción de saltos es la técnica ...

al final de la etapa ID al final de la etapa IF

- Página 84. En la figura 2.55 las fechas que aparecen sobre las etapas ID deberían aparecer sobre las etapas IF pues es en la etapa IF en la que se realiza la predicción de saltos.

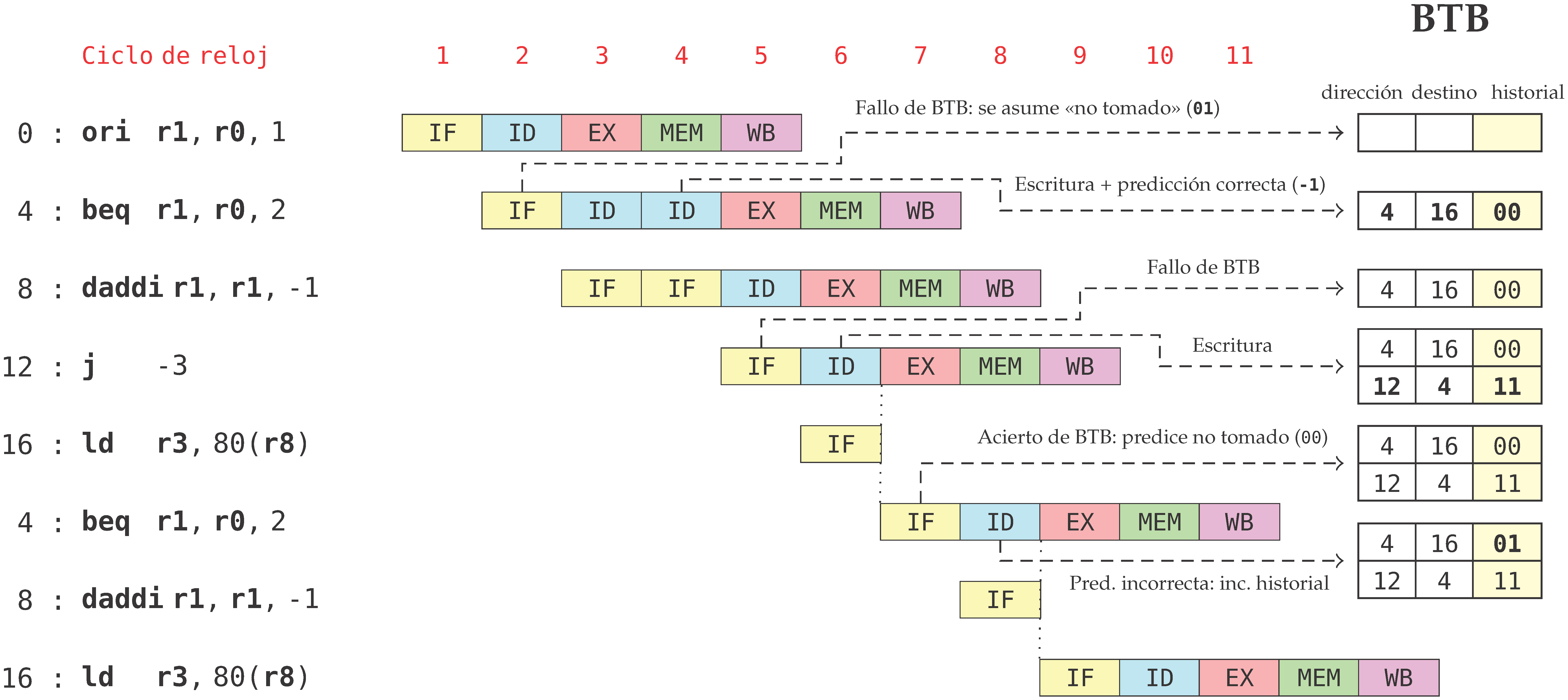

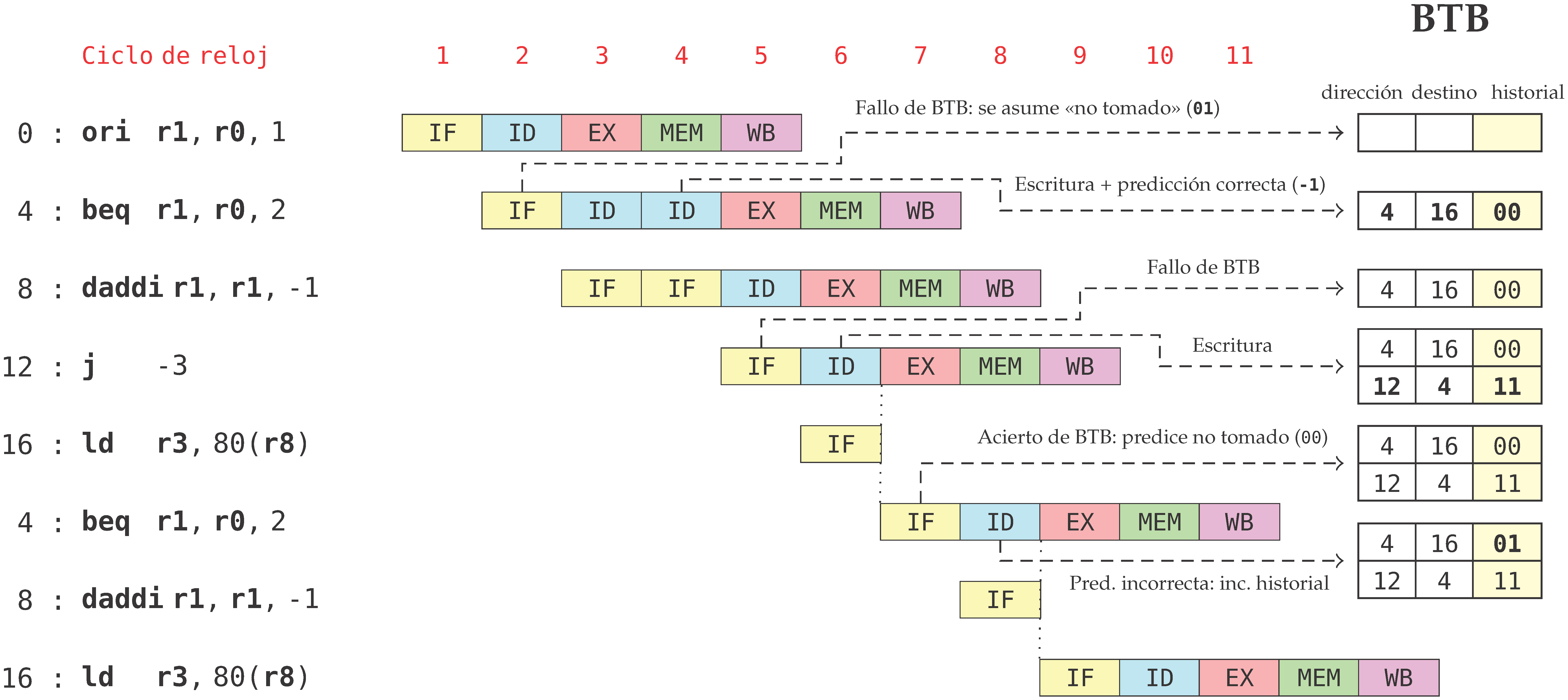

- Página 88. La figura 2.57 es incorrecta. La instrucción inicial debería ser ori r1, r0, 1, que genera una dependencia RAW sobre la instrucción beq r1, r0, 2. Además, el estado inicial del historial no es correcto. A continuación se muestra la figura correcta.

- Página 92. Actualmente, la mayor parte de las CPU ... por lo que

lo que se centrará ...

- Página 109. ... dado que no es capaz de identificar los cambios de ejecución de una tarea a

otro otra.

- Página 122. El coste de la espera de la CPU ... por la necesidad de esperar por la memoria.

- Página 156.En la descripción de la caché L1 de código, en el número de vías pone 82 y debería ser 8.

- Página 175. Las cachés con las que se ha trabajado hasta ahora ... este tipo de cachés

accarrean acarrean una pérdida... - Página 175. Para que la caché pueda cachear... será necesario

invaliar invalidar la caché con cada...

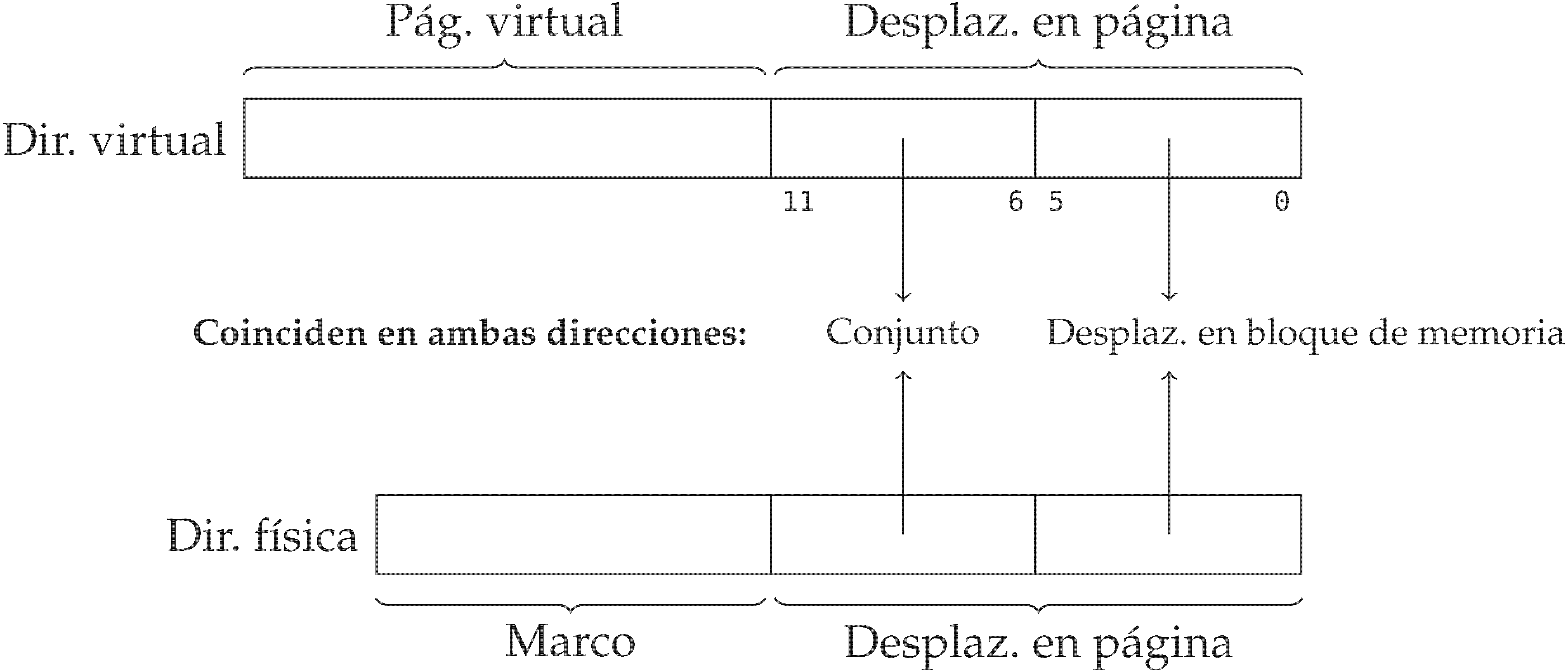

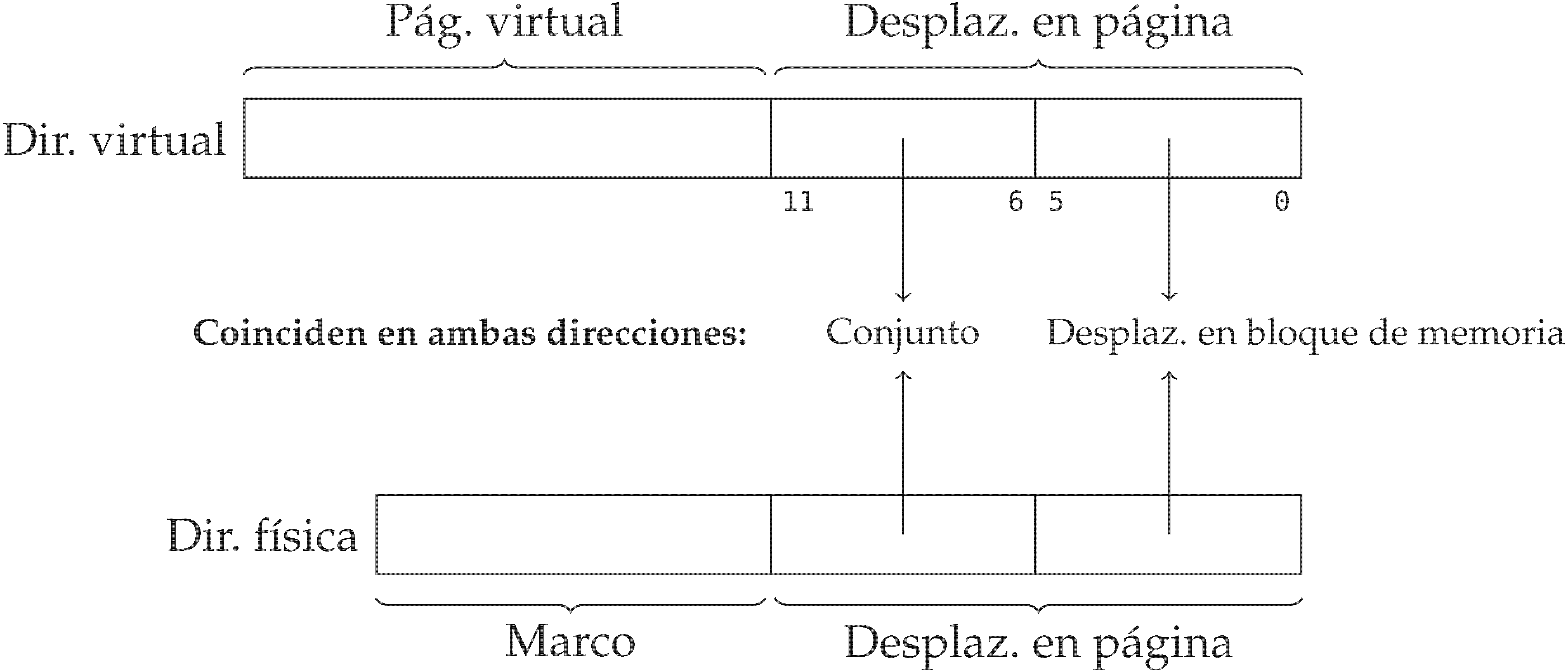

- Página 178. En la figura 3.57 debería aparecer Desplaz. en lugar de Deplaz. Además, el número de bits destinados al conjunto debe ser 6 (y otros 6 para el desplazamiento en el bloque) en lugar de 3. A continuación se muestra la figura correcta.